# CALIBRATION AND SERVICING HANDBOOK

for

# THE DATRON 4200 AUTOCAL AC STANDARD

Volume 1

Calibration and Servicing Information

850056

Issue1 (May 1986)

For any assistance contact your nearest Datron Sales and Service Centre.

Addresses can be found at the back of this handbook.

Due to our policy of continuously updating our products, this handbook may contain minor differences in specification, components and circuit design to the instrument actually supplied. Amendment sheets precisely matched to your instrument serial number are available on request.

# DANGER HIGH VOLTAGE

# THIS INSTRUMENT IS CAPABLE OF DELIVERING A LETHAL ELECTRIC SHOCK!

FRONT or REAR terminals carry the Full Output Voltage.

### THIS CAN KILL!

Guard terminal is sensitive to over-voltage

It can damage your instrument!

it is **safe** to do so,

DO NOT TOUCH the

I+ I- Hi or Lo leads

and **terminals**

DANGER

#### CONTENTS

| GENE    | RAL DI  | ESCRIPTI          | ON                                                   | 1                        |

|---------|---------|-------------------|------------------------------------------------------|--------------------------|

| INST    | ALLATI  | ON                |                                                      |                          |

| CONT    | BOIS A  | ND CON            | NECTIONS                                             | Refer to User's Handbook |

| SDEC    | IEICATI | ON AND            | SPECIFICATION VERIFICATION                           |                          |

|         |         |                   | PLICATIONS                                           |                          |

| OI LII  | ATION   | AND ALL           | Elo/tione                                            | (granse i i              |

| Section | n       |                   | Title                                                | Page                     |

|         |         |                   |                                                      |                          |

| 1       | CALIB   | RATION            |                                                      |                          |

|         | 1.1     | INTRO             | DUCTION                                              | 1–1                      |

|         |         | 1.1.1             | Manufacturer's Initial Calibration                   |                          |

|         |         | 1.1.2             | Need to Recalibrate                                  |                          |

|         |         | 1.1.3             | Recalibration Procedures in this Section             |                          |

|         | 1.2     | ROUTI             | NE AUTOCALIBRATION                                   |                          |

|         |         | 1.2.1             | Introduction                                         |                          |

|         |         | 1.2.2             | The 4200 Autocal Feature                             |                          |

|         |         | 1.2.3             | Equipment Requirements                               |                          |

|         |         | 1.2.4             | Interconnections                                     |                          |

|         |         | 1.2.5             | Calibration Modes                                    |                          |

|         |         | 1.2.6             | General Notes                                        |                          |

|         |         | 1.2.7             | Calibration Sequence                                 |                          |

|         |         | 1.2.8             | AC Voltage Full Range Calibration (IV – 1000V)       |                          |

|         |         | 1.2.9             | AC Voltage — HF 2-wire Compensation (IV & 10V range) | 1–7                      |

|         |         | 1.2.10            | Millivolts (LF) Full Range Calibration (1mV - 100mV) |                          |

|         |         | 1.2.11            | Millivolts (HF) Full Range Calibration (1mV - 100mV) |                          |

|         |         | 1.2.12            | Current Full Range Calibration (1mA – 1A)            | 1–10                     |

|         |         | 1.2.13            | Current Full Range Calibration (100 $\mu$ A – 1A)    | 1–11                     |

|         | 1.3     | REMO <sup>2</sup> | TE CALIBRATION GUIDELINES                            |                          |

|         |         | 1.3.1             | Introduction                                         | 1–12                     |

|         |         | 1.3.2             | Calibration Commands                                 |                          |

|         |         | 1.3.3             | Programming Guidelines                               |                          |

|         | 1.4     | PRE-CA            | ALIBRATION                                           | 1–15                     |

|         |         | 1.4.1             | Validity                                             | 1–15                     |

|         |         | 1.4.2             | Calibration Standards Equipment Required             | 1–15                     |

|         |         | 1.4.3             | Preparation                                          |                          |

|         |         | 1.4.4             | Pre-calibration Procedure                            |                          |

|         |         | 1.4.5             | Remote Pre-Calibration Guidelines                    | 1–18                     |

|         | pm a    |                   |                                                      |                          |

| 2       |         |                   | OSIS                                                 |                          |

|         | 2.1     |                   | DUCTION                                              |                          |

|         |         | 2.1.1             | Use of Diagnostic Guides                             |                          |

|         |         | 2.1.2             | Effects of Protective Measures on Diagnosis          |                          |

|   | 2.2   | DIAGI  | NOSTIC GUIDES                          |

|---|-------|--------|----------------------------------------|

|   |       | 2.2.1  | FAIL 1 Display Message                 |

|   |       | 2.2.2  | FAIL 2 Display Message                 |

|   |       | 2.2.3  | FAIL 3 Display Message                 |

|   |       | 2.2.4  | FAIL 4 Display Message                 |

|   |       | 2.2.5  | FAIL 5 Display Message                 |

|   |       | 2.2.6  | FAIL 6 Display Message                 |

|   |       | 2.2.7  | FAIL 7 Display Message                 |

|   |       | 2.2.8  | FAIL 8 Display Message                 |

|   |       | 2.2.9  | FAIL 9 Display Message                 |

|   |       | 2.2.10 | Error OL Display Message               |

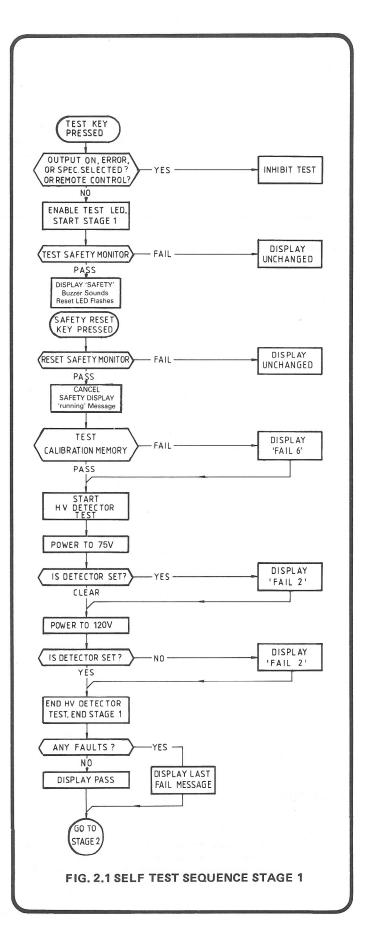

|   | 2.3   | SELF-1 | TEST SEQUENCE                          |

|   |       | 2.3.1  | General                                |

|   |       | 2.3.2  | Stage 1                                |

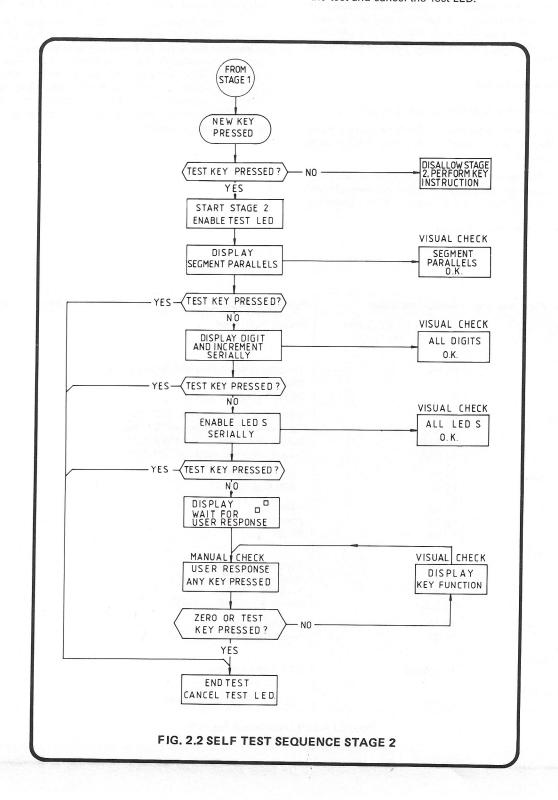

|   |       | 2.3.3  | Stage 2                                |

|   | 2.4   | FUSE F | PROTECTION                             |

|   |       | 2.4.1  | Fuse Replacement                       |

|   |       | 2.4.2  | Reasons For Fusing                     |

|   |       | 2.4.3  | Locating a Blown Fuse                  |

|   |       |        |                                        |

|   |       |        |                                        |

| 3 | DISMA |        | AND REASSEMBLY                         |

|   | 3.1   | GENER  | RAL PRECAUTIONS                        |

|   |       | 3.1.1  | Warnings                               |

|   |       | 3.1.2  | Cautions                               |

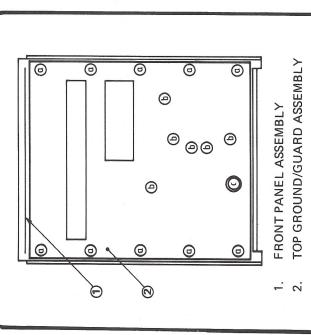

|   | 3.2   | GENEF  | RAL MECHANICAL LAYOUT3-1               |

|   |       | 3.2.1  | Front Panel                            |

|   |       | 3.2.2  | Rear Panel                             |

|   | 3.3   |        | TION AND ACCESS                        |

|   |       | 3.3.1  | External Construction                  |

|   |       | 3.3.2  | Internal Construction                  |

|   | 3.4   |        | RAL ACCESS                             |

|   |       | 3.4.1  | Top Cover Removal                      |

|   |       | 3.4.2  | Top Cover Fitting                      |

|   |       | 3.4.3  | Bottom Cover Removal                   |

|   |       | 3.4.4  | Bottom Cover Fitting                   |

|   |       | 3.4.5  | Front Panel — Removal                  |

|   |       | 3.4.6  | Front Panel — Fitting                  |

|   |       | 3.4.7  | Top Ground/Guard Assembly Removal      |

|   |       | 3.4.8  | Top Ground/Guard Assembly Fitting      |

|   |       | 3.4.9  | Bottom Ground Sheet Assembly — Removal |

|   |       | 3.4.10 | Bottom Ground Sheet Assembly — Fitting |

|   |       | 3.4.11 | Bottom Guard Plate — Removal           |

|   |       | 3.4.12 | Bottom Guard Plate — Fitting           |

|   | 3.5   |        | /AL AND FITTING INSTRUCTIONS           |

|   |       | 3.5.1  | Instruction Card                       |

|   |       | 3.5.2  | Front Assembly — Removal               |

|   |       | 3.5.3  | Front Assembly — Fitting               |

|   |       | 3.5.4  | Major PCB Assemblies — Removal         |

|    |       | 3.5.5    | Major PCB Assemblies — Fitting             | .3-5   |

|----|-------|----------|--------------------------------------------|--------|

|    |       | 3.5.6    | Common, Guard and Ground Screens — Removal | .3–5   |

|    |       | 3.5.7    | Common, Guard and Ground Screens — Fitting |        |

|    |       | 3.5.8    | Power Amplifier Assembly — Removal         |        |

|    |       | 3.5.9    | Power Amplifier Assembly — Fitting         |        |

|    |       | 3.5.10   | Out-Guard Power Supply Assembly — Removal  |        |

|    |       | 3.5.11   | Out-Guard Power Supply Assembly — Fitting  |        |

|    |       | 3.5.11   | In-Guard Power Supply Assembly — Removal   |        |

|    |       | 3.5.12   | In-Guard Power Supply Assembly — Fitting   |        |

|    |       |          |                                            |        |

|    |       | 3.5.14   | ±38V Power Supply — Removal                |        |

|    |       | 3.5.15   | ±38V Power Supply — Fitting                |        |

|    |       | 3.5.16   | Heatsink Assemblies – Removal              |        |

|    |       | 3.5.17   | Heatsink Assembly — Fitting                |        |

|    |       | 3.5.18   | High Voltage Assembly — Removal            |        |

|    |       | 3.5.19   | High Voltage Assembly — Fitting            |        |

|    |       | 3.5.20   | Line Transformer Assembly — Removal        |        |

|    |       | 3.5.21   | Line Transformer Assembly — Fitting        |        |

|    |       | 3.5.22   | HF Transformer Assembly — Removal          | 3–7    |

|    |       | 3.5.23   | HF Transformer Assembly — Fitting          | 3–7    |

|    |       | 3.5.24   | LF Transformer Assembly — Removal          | 3–8    |

|    |       | 3.5.25   | LF Transformer Assembly — Fitting          | .3–8   |

|    |       | 3.5.26   | Terminal PCB Assembly — Removal            | 3–8    |

| ,  |       | 3.5.27   | Terminal PCB Assembly – Fitting            |        |

|    |       | 3.5.28   | Rear Panel Assembly – Removal              |        |

|    |       | 3.5.29   | Rear Panel Assembly — Fitting              |        |

|    |       |          |                                            |        |

|    |       |          |                                            |        |

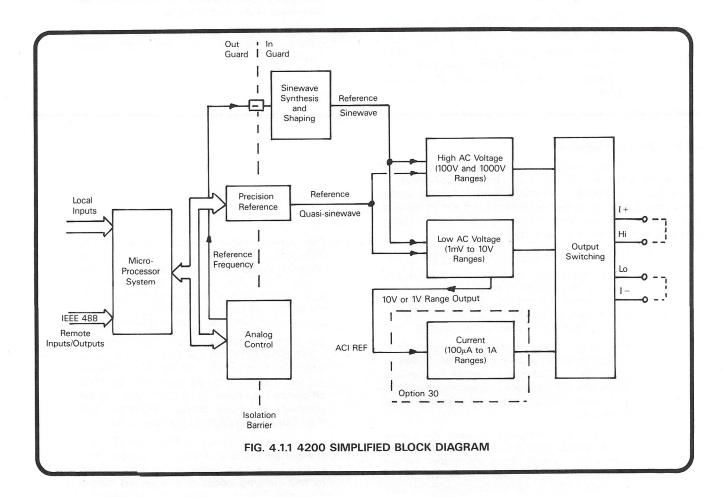

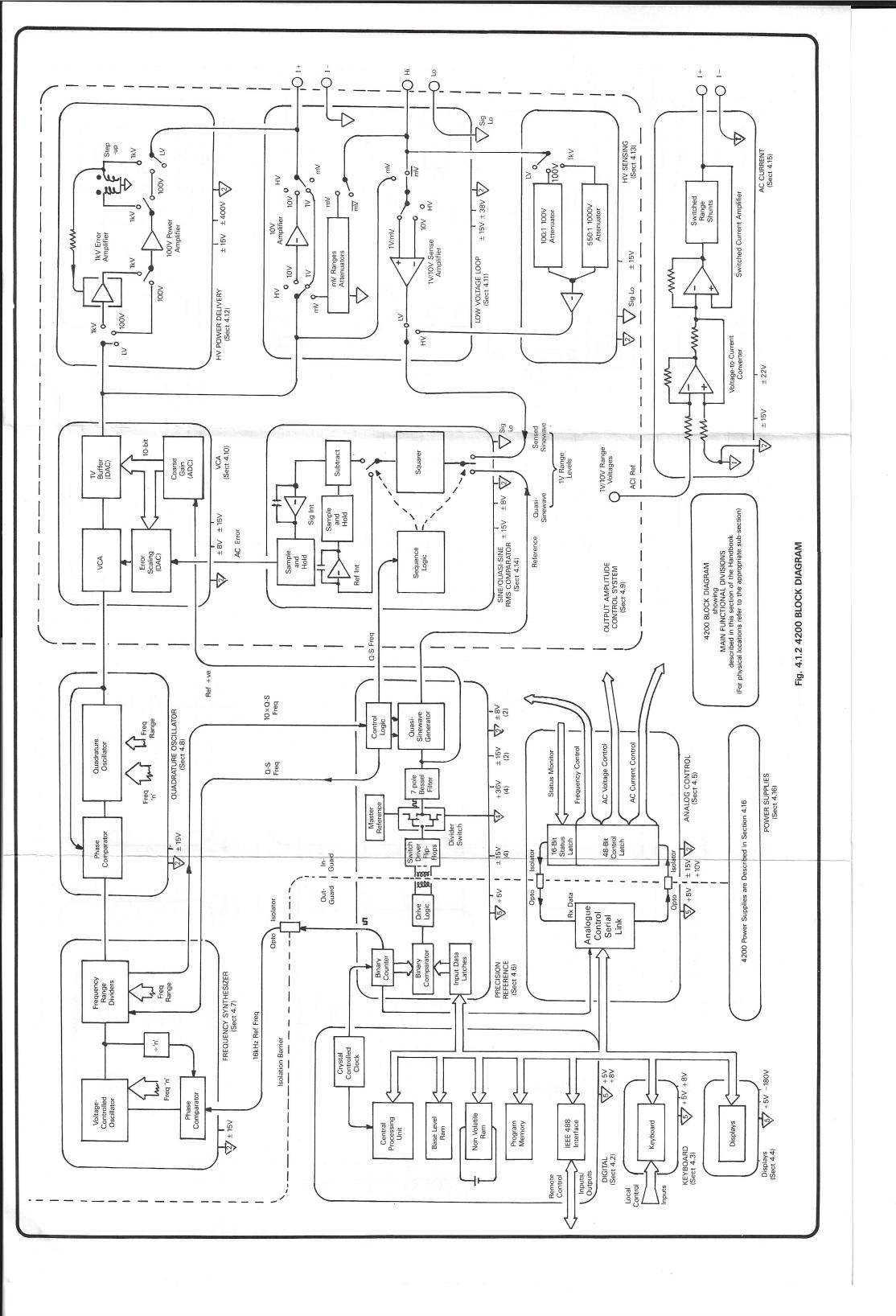

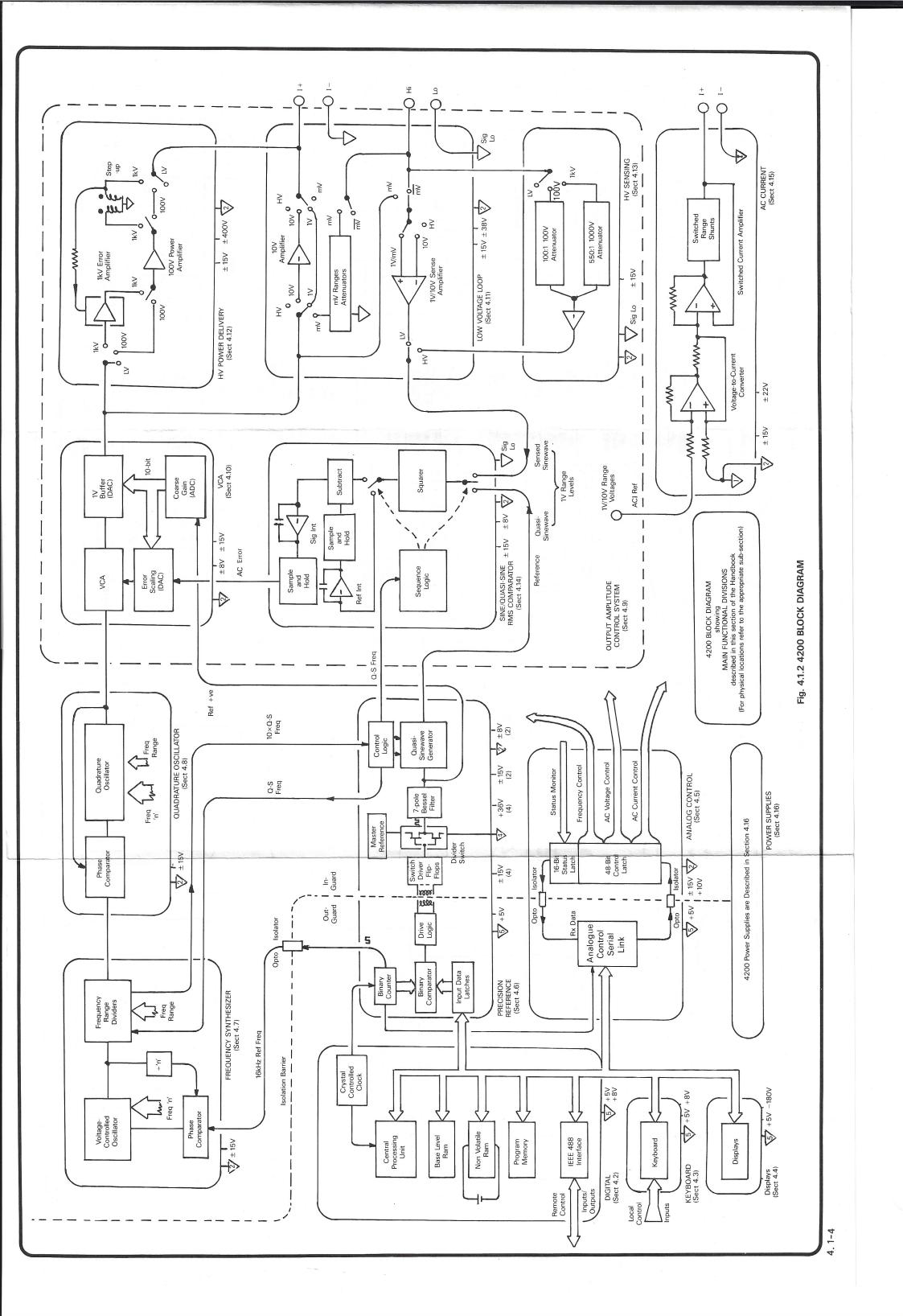

| 4. | TECHN | IICAL DI | ESCRIPTION                                 | 4. 1–1 |

|    | 4.1   | PRINCI   | IPLES OF OPERATION                         | 4. 1–1 |

|    |       | 4.1.1    | Inputs                                     |        |

|    |       | 4.1.2    | Digital Outputs                            |        |

|    |       | 4.1.3    | Precision Reference                        |        |

|    |       | 4.1.4    | Analog Control                             |        |

|    |       | 4.1.5    | Sinewave Synthesis and Shaping             |        |

|    |       | 4.1.6    | Low AC Voltage Output                      |        |

|    |       | 4.1.7    | High AC Voltage Loop                       |        |

|    |       | 4.1.8    | Current Output (Option 20)                 |        |

|    |       | 4.1.9    | 'AUTOCAL'4                                 |        |

|    | 4.2   |          | AL                                         |        |

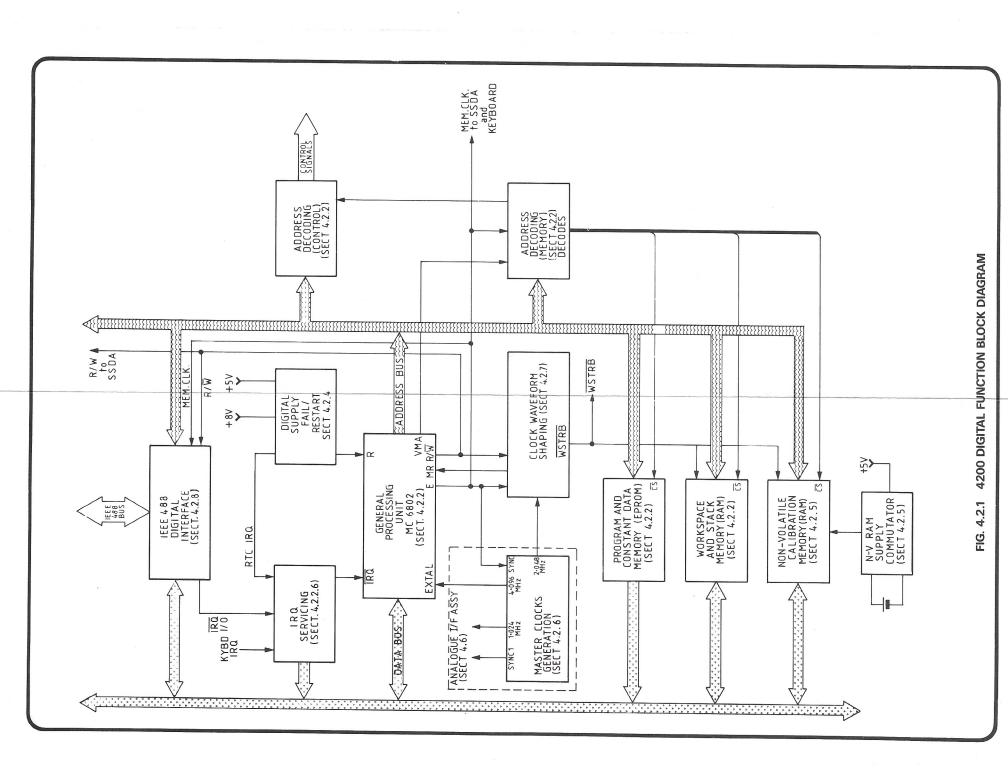

|    | 4.2   | 4.2.1    | General                                    |        |

|    |       | 4.2.1    |                                            |        |

|    |       | 4.2.2    | Central Processor and Memory               |        |

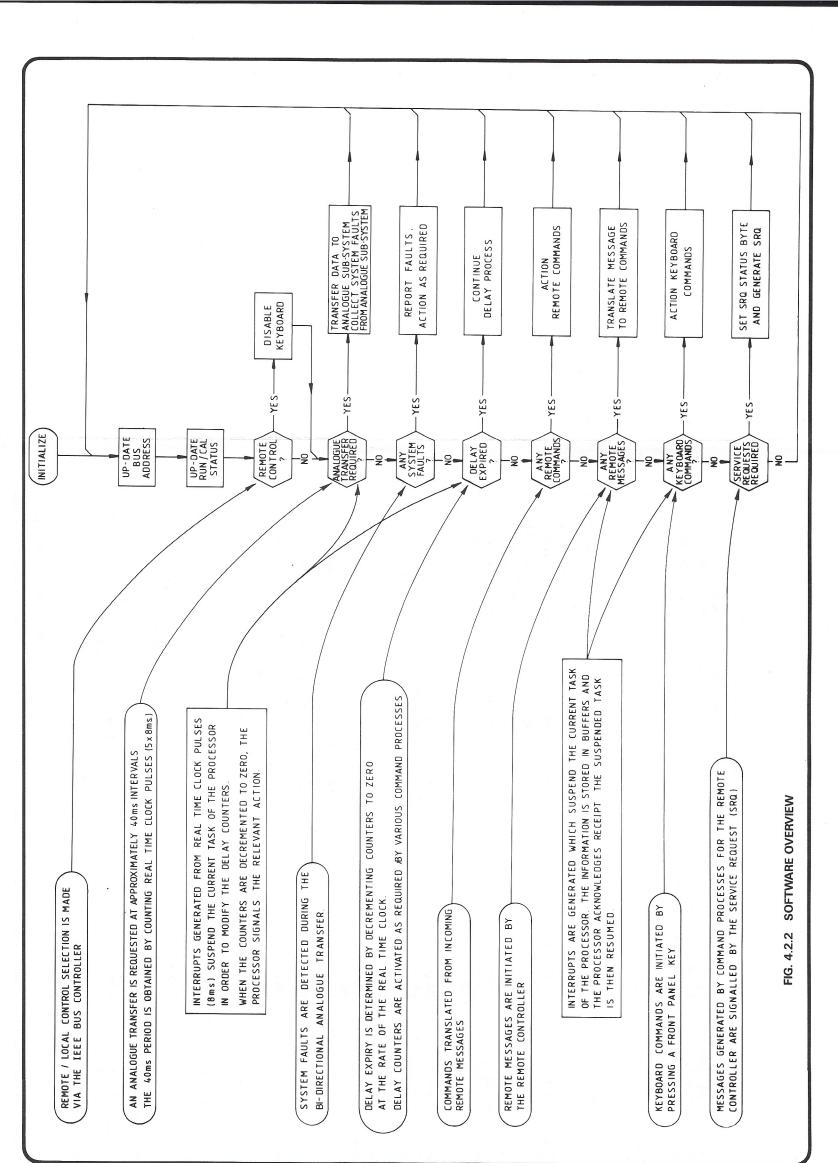

|    |       |          | Software Overview                          |        |

|    |       | 4.2.4    | Digital Supply Fail/Restart Circuitry      |        |

|    |       | 4.2.5    | Non-Volatile RAM Supply Commutation        |        |

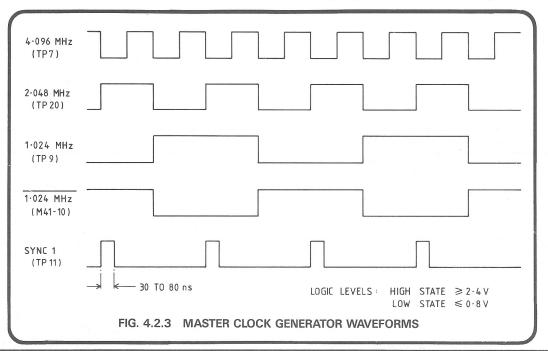

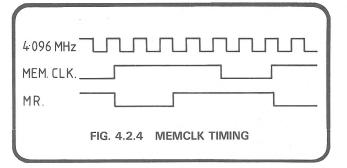

|    |       | 4.2.6    | Master Clock Generation                    |        |

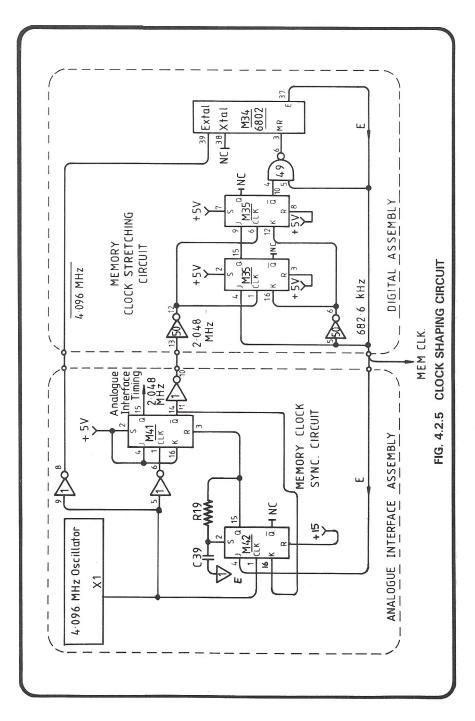

|    |       | 4.2.7    | Clock Waveform Shaping                     |        |

|    |       | 4.2.8    | IEEE 488 Digital Interface                 |        |

|    | 4.3   |          | DARD                                       |        |

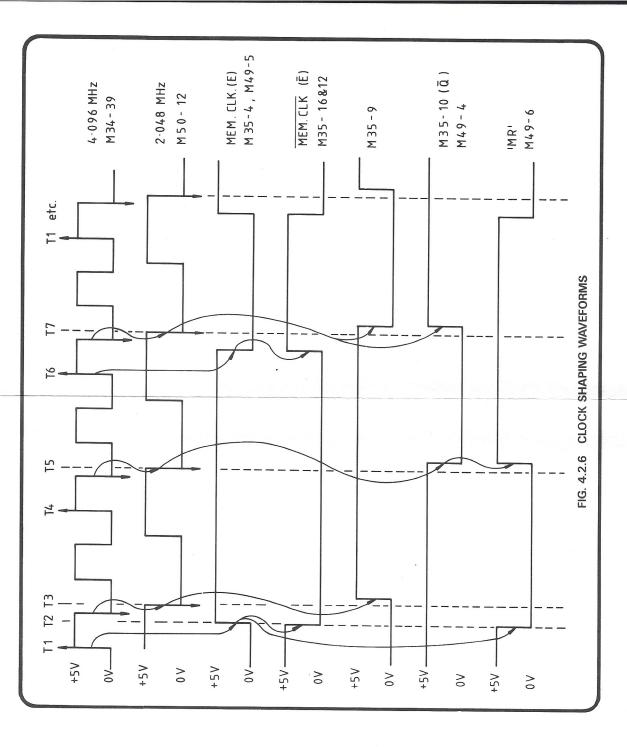

|    |       | 4.3.1    | Key and LED Matrices                       | 2 1    |

|     | 4.3.2  | Programmable Interfere MG           | 4 0 4 |

|-----|--------|-------------------------------------|-------|

|     |        | Programmable Interface M6           |       |

|     | 4.3.3  | Scan Decoding                       |       |

|     | 4.3.4  | Key Selection                       |       |

|     | 4.3.5  | Key LED Operation                   |       |

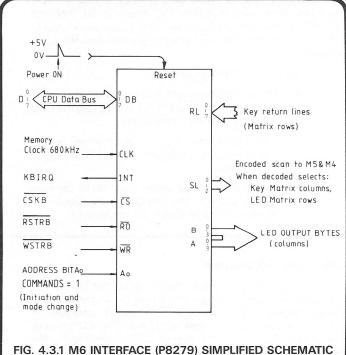

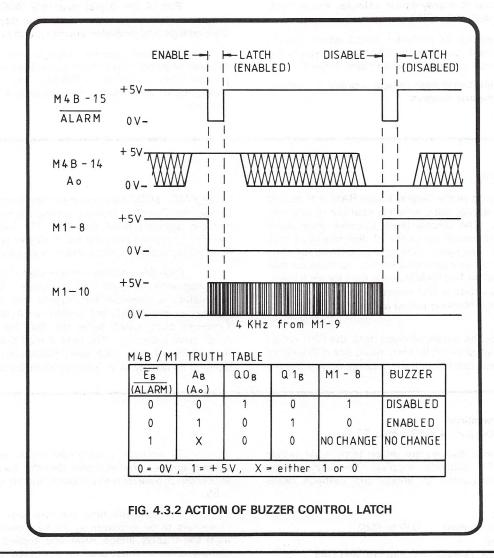

|     | 4.3.6  | Audible Warning Buzzer              |       |

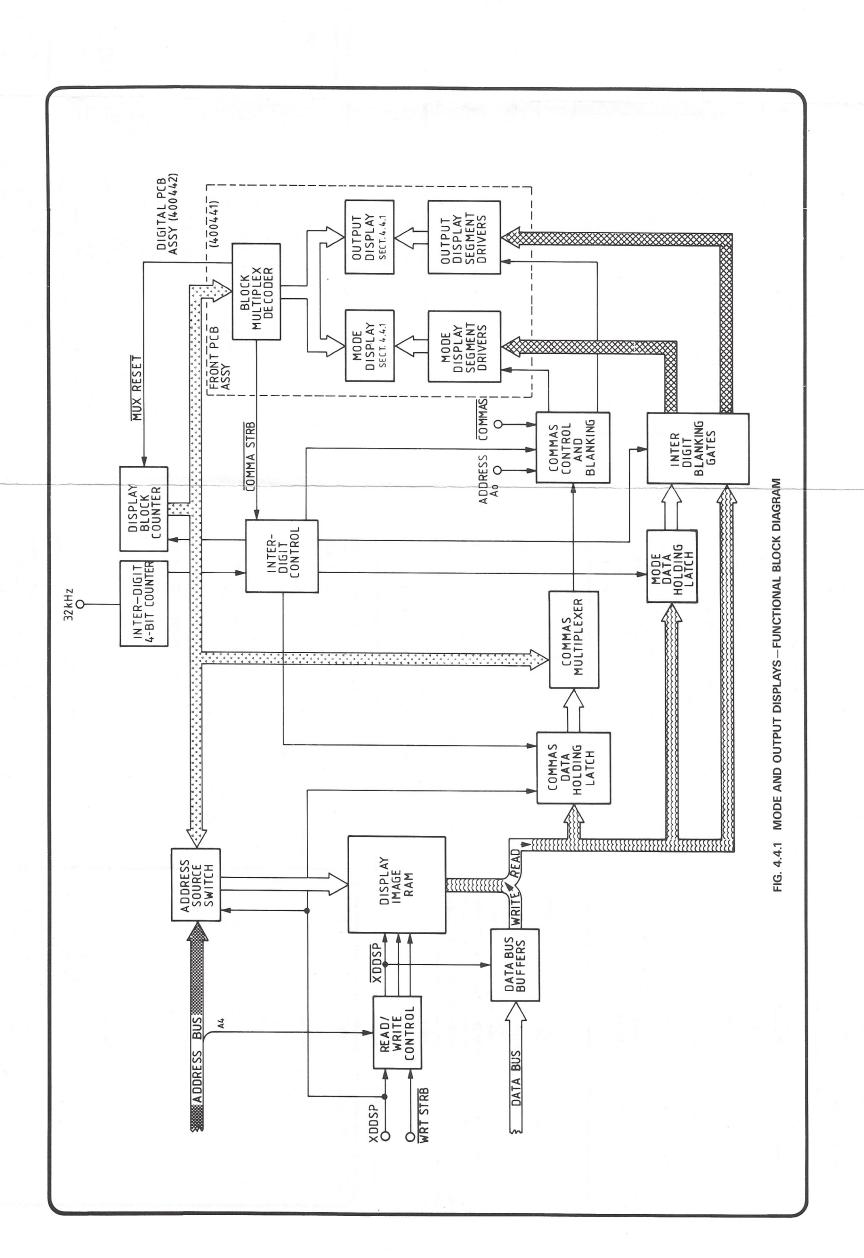

| 4.4 |        | AL DISPLAYS                         |       |

|     | 4.4.1  | General                             | 4.4-0 |

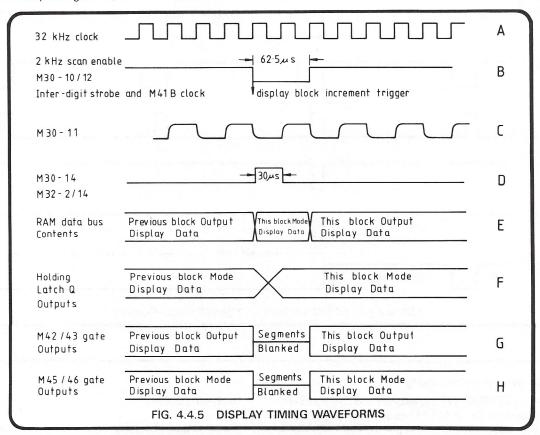

|     | 4.4.2  | Static Conditions                   | 4.4-0 |

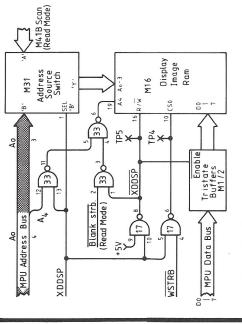

|     | 4.4.3  | Write Mode                          | 4.4-2 |

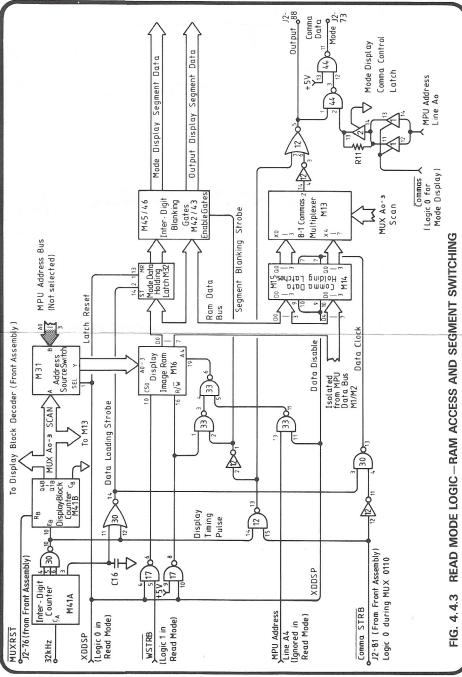

|     | 4.4.4  | Read Mode                           | 4.4-2 |

| 4.5 | ANALO  | OG CONTROL INTERFACE                | 4.5-0 |

|     | 4.5.1  | General                             | 4.5-0 |

|     | 4.5.2  | Serial Data Transfer                | 4.5-0 |

|     | 4.5.3  | Synchronous Serial Data Adaptor     | 4.5-1 |

|     | 4.5.4  | SSDA Clock Generation               |       |

|     | 4.5.5  | Serial/Parallel Data Converter      | 4.5-4 |

|     | 4.5.6  | Safety Monitor (Watchdog)           |       |

| 4.6 | PRECIS | SION DIVIDER                        |       |

|     | 4.6.1  | Precision Divider Comparators       |       |

|     | 4.6.2  | Comparator Circuit Action           |       |

|     | 4.6.3  | References and Reference Divider.   |       |

|     | 4.6.4  | Master Reference                    |       |

|     | 4.6.5  | Reference Buffer-Divider            |       |

|     | 4.6.6  | Least-Significant-Digits Switching. |       |

|     | 4.6.7  | Most-Significant-Digits Switching   |       |

|     | 4.6.8  | Main and Guard Switches             |       |

|     | 4.6.9  | 7-Pole Filter                       |       |

|     | 4.6.10 | Summing Amplifer                    |       |

|     | 4.6.11 | Quasi-Sinewave Generation           |       |

| 4.7 |        | AL FREQUENCY SYNTHESIZER            |       |

| 4.7 |        |                                     |       |

|     | 4.7.1  | General                             |       |

|     | 4.7.2  | Voltage Controlled Oscillator       |       |

|     | 4.7.3  | Frequency Range Dividers            |       |

| 4.8 |        | RATURE SINEWAVE OSCILLATOR          |       |

|     | 4.8.1. | Purpose and Environment             |       |

|     | 4.8.2  | Simple Quadrature Oscillator        |       |

|     | 4.8.3  | Practical Quadrature Oscillator     |       |

|     | 4.8.4  | Frequency Control                   |       |

|     | 4.8.5  | Oscillator Output                   |       |

|     | 4.8.6  | Main Integrators                    |       |

|     | 4.8.7  | Inverter Stage                      |       |

|     | 4.8.8  | Oscillation Amplitude Detector      |       |

|     | 4.8.9  | Amplitude Control Implementation    | 4.8–8 |

| 4.9 | OUTPU  | JT AMPLITUDE CONTROL SYSTEM         | 4.9-1 |

|     | 4.9.1  | System Block Diagram                | 4.9-2 |

|     | 4.9.2  | Frequency and Waveshape Control     | 4.9-2 |

|     | 4,9,3  | Output Ranging                      | 4.9-2 |

|     | 4.9.4  | Coarse Amplitude Setting            | 4.9-2 |

|     | 4.9.5  | Fine Amplitude Control              | 4.9-2 |

| 4.10 | VOLTA              | GE CONTROLLED AMPLIFIERS                        | . 10–1  |

|------|--------------------|-------------------------------------------------|---------|

|      | 4.10.1             | General                                         | . 10–1  |

|      | 4.10.2             | Main Voltage-Controlled Amplifier               | . 10–2  |

|      | 4.10.3             | The 1V Buffer                                   |         |

|      | 4.10.4             | Current Detector4                               | . 10–3  |

|      | 4.10.5             | ADC - DAC Tracking                              | . 10–3  |

| 4.11 |                    | OLTAGE LOOP                                     | . 11–1  |

| 8    | 4.11.1             | General                                         | . 11–2  |

|      | 4.11.2             | 1V Loop — Power Delivery                        | . 11–2  |

|      | 4.11.3             | 1V Loop — Output Sensing                        | . 11–3  |

|      | 4.11.4             | 1V Sense Amplifier                              | . 11–4  |

|      | 4.11.5             | Millivolt Loop                                  | . 11–4  |

|      | 4.11.6             | 10V Loop                                        | . 11–5  |

|      | 4.11.7             | 10V Power Amplifier                             | . 11–5  |

|      | 4.11.8             | 10V Sense Amplifier                             |         |

|      | 4.11.9             | AC Assembly Logic and Relay Drives              |         |

|      |                    | Output Control Assembly, Logic and Relay Drives | . 11–8  |

|      | 4.11.10<br>1/11/11 | High Voltage Status Detector                    | . 11–9  |

|      | 4.11.11            | 2 Overvoltage Detector                          | . 11–9  |

| 4.10 |                    | OUTAGE POWER DELIVERY4                          |         |

| 4.12 | 4.12.1             | 100V Range Power Routing                        |         |

|      |                    | 100V Power Amplifier                            |         |

|      | 4.12.2             | Gain and Driver Stages                          |         |

|      | 4.12.3             | 100V Buffer Output Stage                        | 12-3    |

|      | 4.12.4             | 1000V Range Power Routing                       |         |

|      | 4.12.5             |                                                 |         |

|      | 4.12.6             | 1kV Power Amplifier                             |         |

|      | 4.12.7             | Power Supplied and Protection                   |         |

|      | 4.12.8             | PA Power Supply Monitors                        |         |

|      | 4.12.9             | PA Logic and Relay Drives                       |         |

| 4.13 |                    | VOLTAGE SENSING                                 |         |

|      | 4.13.1             | 100V Sense Amplifier                            |         |

|      | 4.13.2             | 1000V Sense Amplifier                           |         |

| 4.14 | SINE/Q             | QUASI-SINE RMS COMPARATOR                       |         |

|      | 4.14.1             | Purpose and Environment                         |         |

|      | 4.14.2             | Implementation                                  |         |

|      | 4.14.3             | Method of Comparison4                           |         |

|      | 4.14.4             | Comparator Control Logic                        |         |

|      | 4.14.5             | Comparator Timing Logic                         |         |

|      | 4.14.6             | Square Law Detector Circuit                     |         |

|      | 4.14.7             | Generation of the DC Subtraction Current        |         |

|      | 4.14.8             | 'AC ERROR' Signal Generation                    |         |

| 4.15 | CURRE              | ENT (Option 30)                                 |         |

|      | 4.15.1             | Basic Voltage-to-Current Converter              |         |

|      | 4.15.2             | Two-stage Current Generator4                    | 1. 15–1 |

|      | 4.15.3             | Current Reference 'PHI (ACI REF)'               |         |

|      | 4.15.4             | Range Selection                                 | 1. 15–2 |

|      | 4.15.5             | Voltage-to-Current Converter                    | 1. 15–3 |

|      | 4.15.6             | Voltage Preamplifier                            | . 15–3  |

|      | 4 15 7             | High Current Output Stage                       | 15_3    |

|   |        | 4.15.8  | Output Protection                   | 1 - 1 |

|---|--------|---------|-------------------------------------|-------|

|   | 4.16   |         |                                     |       |

|   | 4.10   | 4.16.1  | R SUPPLIES                          |       |

|   |        | 4.16.2  | Out-Guard Power Supplies            |       |

|   |        | 4.16.3  | In-Guard Power Supplies             |       |

|   |        |         | dana i diver dappines               | 10-2  |

| 5 | SERVIO | ING AN  | D INTERNAL ADJUSTMENTS              | E 1   |

|   | 5.1    |         | DUCTION                             |       |

|   | 0.1    | 5.1.1   | General                             |       |

|   | 5.2    | _,,,,,  | ING THE AIR INTAKE FILTER           |       |

|   | 0.2    | 5.2.1   | Servicing Frequency                 |       |

|   |        | 5.2.2   | Removal                             |       |

|   |        | 5.2.3   | Cleaning                            |       |

|   |        | 5.2.4   | Inspection                          |       |

|   |        | 5.2.5   | Reassembly                          |       |

|   | 5.3    |         | M BATTERY                           |       |

|   |        | 5.3.1   | Procedure                           |       |

|   |        | 5.3.2   | Return to Use                       |       |

|   | 5.4    | ±120 V0 | DLTS                                |       |

|   |        | 5.4.1   | Test Equipment Required             |       |

|   |        | 5.4.2   | Initial Conditions                  |       |

|   |        | 5.4.3   | Procedure                           |       |

|   |        | 5.4.4   | Return to Use                       |       |

|   | 5.5    | CAPACI  | ITIVE LOAD TEST                     |       |

|   |        | 5.5.1   | Test Equipment Required             |       |

|   |        | 5.5.2   | Initial Conditions                  |       |

|   |        | 5.5.3   | Procedure                           |       |

|   |        | 5.5.4   | Return to Use                       | 5-5   |

|   | 5.6    | CURRE   | NT PCB QUIESCENT CURRENT ADJUSTMENT | 5–6   |

|   |        | 5.6.1   | Test Equipment Required             | 56    |

|   |        | 5.6.2   | Initial Conditions                  | 5-6   |

|   |        | 5.6.3   | Procedure                           | 5-6   |

|   |        | 5.6.4   | Return to Use                       | 5-6   |

|   | 5.7    | COMPL   | IANCE ADJUSTMENT                    | 5-7   |

|   |        | 5.7.1   | Test Equipment Required             | 5-7   |

|   |        | 5.7.2   | Initial Conditions                  | 5-7   |

|   |        | 5.7.3   | Procedure                           | 5-7   |

|   |        | 5.7.4   | Return to Use                       | 5-7   |

|   | 5.8    |         | ON MODE NULL ADJUSTMENTS            | 5-8   |

|   |        | 5.8.1   | Test Equipment Required             |       |

|   |        | 5.8.2   | Initial Conditions                  |       |

|   |        | 5.8.3   | Procedure                           |       |

|   |        | 5.8.4   | Return to Use                       |       |

|   | 5.9    |         | AMPLIFIER ZEROS                     |       |

|   |        | 5.9.1   | Test Equipment Required             |       |

|   |        | 5.9.2   | Initial Conditions                  |       |

|   |        | 5.9.3   | Procedure                           |       |

|   |        | 5.9.4   | Return to Use                       | 5–9   |

#### ILLUSTRATIONS

| Figure | Title                                                            | Page   |

|--------|------------------------------------------------------------------|--------|

| 1.1    | Calibration Modes                                                | 1–4    |

| 1.2    | Transfer of Calibration Facilities to Remote Control             | 1–13   |

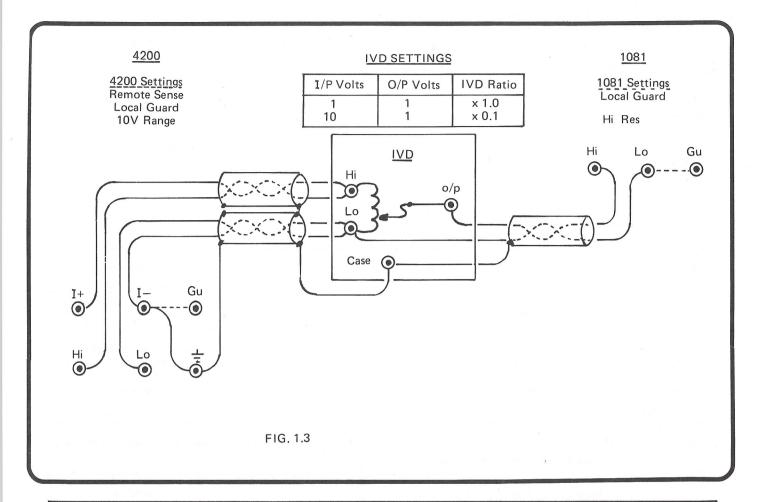

| 1.3    | Interconnections for Precalibration                              | 1–16   |

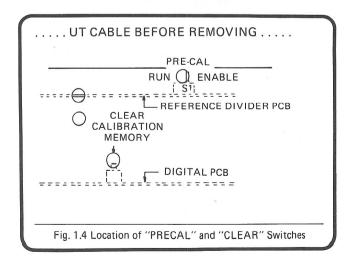

| 1.4    | Location of "PRECAL" and "CLEAR" Switches                        | 1–16   |

| 1.5    | Precalibration — Use of Manual Keys                              | 1–17   |

| 1.6    | Transfer of Precalibration to Remote Control                     |        |

| 2.1    | Self Test Sequence Stage 1                                       |        |

| 2.2    | Self Test Sequence Stage 2                                       |        |

| 3.4.1  | Fitting Top Ground/Guard                                         |        |

| 3.4.2  | Fitting Bottom Ground/Guard                                      |        |

| 4.1.1  | 4200 Simplified Block Diagram                                    | 4. 1–1 |

| 4.1.2  | 4200 Block Diagram                                               | 4. 1–3 |

| 4.2.1  | 4200 Digital Function Block Diagram                              |        |

| 4.2.2  | Software Overview                                                |        |

| 4.2.3  | Master Clock Generator Waveforms                                 | 4. 2–6 |

| 4.2.4  | MEMCLK Timing                                                    | 4. 2–6 |

| 4.2.5  | Clock Shaping Circuit                                            |        |

| 4.2.6  | Clock Shaping Waveforms                                          | 4. 2–7 |

| 4.9    | 2.048MHz Clock Phase-synchronisation                             |        |

| 4.3.1  | M6 Interface (P8279) Simplified Schematic                        |        |

| 4.3.2  | Action of Buzzer Control Latch                                   |        |

| 4.4.1  | Mode and Output Displays — Functional Block Diagram              | 4. 4–1 |

| 4.4.2  | RAM Access – Write Mode Logic                                    | 4. 4–2 |

| 4.4.3  | Read Mode Logic — RAM Access and Segment Switching               | 4. 4–2 |

| 4.4.4  | Display Scan Energizing Sequence                                 |        |

| 4.4.5  | Display Timing Waveforms                                         | 4. 4–3 |

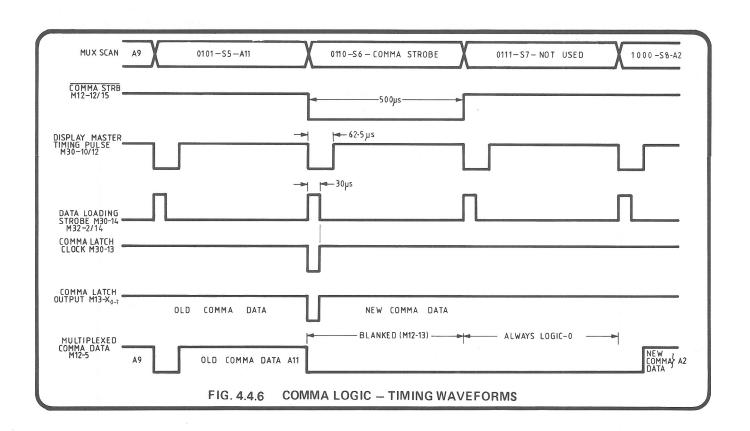

| 4.4.6  | Comma Logic — Timing Waveforms                                   | 4. 4–4 |

| 4.5.1  | Serial Data Link — Simplified Functional Block Diagram           | 4. 5–0 |

| 4.5.2  | Serial Data Transfer Organization                                | 4. 5–1 |

| 4.5.3  | SSDA Clock Generator Waveforms                                   |        |

| 4.5.4  | Watchdog Circuitry — Simplified Block Diagram                    | 4. 5–5 |

| 4.6.1  | Precision Divider Out-Guard Circuitry — Simplified Block Diagram |        |

| 4.6.2  | Precision Divider In-Guard Circuitry — Simplified Block Diagram  |        |

| 4.6.3  | 13-Bit Counter Waveforms                                         |        |

| 4.6.4  | 'BUSY' Waveforms                                                 |        |

| 4.6.5  | MSB Sync Logic Waveforms                                         |        |

| 4.6.6  | MSB Set/Reset Pulse Generation                                   |        |

| 4.6.7  | LSB Set/Reset Pulse Generation                                   |        |

| 4.6.8  | Basic Reference Circuit                                          |        |

| 4.6.9  | Action of LSD Switch                                             |        |

| 4.6.10 | Action of Main and Guard Switches (MSD)                          |        |

| 4.6.11 | Quasi — Sine Wave Generator                                      |        |

| 4.7.1  | Frequency Synthesizer Block Diagram                              |        |

| 4.7.2  | V.C.O. Block Diagram                                             |        |

| 4.7.3  | Frequency Dividers Block Diagram                                 |        |

| 4.8.1. | The Quadrature Sinewave Oscillator and its System Environment    |        |

| 4.8.2. | Basic Quadrature Oscillator                                      |        |

| 4.8.3  | Gain and Phase Response of Practical Circuit                     | 4. 8–2 |

| igure  | Title                                                        | Page     |

|--------|--------------------------------------------------------------|----------|

| 4.8.4  | Corrected Quadrature Oscillator                              | 4. 8–3   |

| 4.8.5  | Fine Frequency Control                                       | 4.8–4    |

| 4.8.6  | Summing $A^2 sin^2 \omega t$ with $A^2 cos^2 \omega t$       |          |

| 4.9.1  | Output Amplitude Control System                              |          |

| 4.10.1 | VCA — Block Diagram                                          |          |

| 4.10.2 | IV Buffer-Output Stage                                       | 4. 10–2  |

| 4.10.3 | Simplified Diagram of Tracking Analogue-to-digital Converter |          |

| 4.10.4 | A-D Tracking — R/2R Network                                  |          |

| 4.10.5 | Window Comparator Action                                     |          |

| 4.11.1 | Low Voltage Loop — Simplified Block Diagram and Routing      | 4. 11–1  |

| 4.11.2 | Millivolt Attenuators                                        | 4. 11–5  |

| 4.12.1 | LIM ST Signal Origins                                        | 4. 12–10 |

| 4.14.1 | The Sine/Quasi-sine Comparator and its Systems Environment   | 4. 14–1  |

| 4.14.2 | Sine/Quasi-sine Comparator — Block Diagram                   | 4. 14–2  |

| 4.14.3 | Sine/Quasi-sine Comparator — Sequence Cycle                  | 4. 14–2  |

| 4.14.4 | Sine/Quasi-sine Comparator — Sequence Timing                 |          |

| 4.14.5 | Comparator Logic Waveforms                                   | 4. 14–5  |

| 4.14.6 | Three Stages of Output Build-up from Zero                    |          |

| 4.15.1 | Basic Voltage-to-Current Converter                           | 4. 15–1  |

| 4.15.2 | The 4200 Current Generator                                   |          |

| 4.15.3 | Current Range Configurations                                 | 4. 15–2  |

| 4.16.1 | Power Distribution Block Diagram                             |          |

| 5.1    | Digital PCB Battery Replacement                              |          |

#### **CALIBRATION**

#### 1.1 INTRODUCTION

#### 1.1.1

#### Manufacturer's Initial Calibration

The 4200 is fully calibrated before leaving the factory, and remains within the appropriate specification for the time periods detailed in Section 6 of the User's Handbook.

#### Caution

Removal of the Top Ground/Guard Assembly invalidates the manufacturer's calibration certification.

#### 1.1.2 Need to Recalibrate

Sections 1.2 to 1.5 detail the procedures necessary to recalibrate instrument functions to known specifications. The occasions for recalibration are as follows:

#### 1. PERIODIC ROUTINE AUTOCALIBRATION

The specifications for the 4200 are based on standard intervals of up to 24 hours, 90 days or 1 year from calibration. Users may wish to choose alternative schemes, accounting for:

- The accuracy required when in use,

- b. The scheduled calibration intervals normally adopted by the user's organization, and

- c. The instrument specifications (User's Handbook Section 6)

#### 2. RE-STANDARDIZATION

Occasions may arise when it is necessary to trim the instrument's internal Master Reference.

For example, when the 4200 is to be made traceable to a different National Standard, after transportation from one country to another.

The procedure for "STD" autocalibration is detailed in Section 1.2.8.

(Refer to Section 1.2.8, para 3, note C).

#### SPOT FREQUENCIES

The 4200 stores the spot frequencies, and their amplitude corrections, in memories which are separate from those used for wideband corrections.

Enhanced accuracy is obtained as any flatness errors in the wideband correction are eliminated. Accuracy tables are given in Section 6 of the User's Handbook, with an example showing Spot F linearity.

#### 4. BATTERY CHANGE

The Lithium battery which powers the non-volatile calibration memory should be replaced after 5 years (Refer to Section 5.3).

After replacement, a full Pre-calibration is required (Section 1.4) followed by a Routine Autocalibration (Section 1.2).

#### 5. CRITICAL PARTS

Recalibration (or Verification) is necessary after replacement of a critical PCB assembly or a critical component.

These are listed in Table 1.1, indicating the extent of the recalibration necessary.

#### 1.1.3 Recalibration Procedures in this Section

(See Section 7 of the User's Handbook for Verification Procedures).

#### **Routine Autocalibration**

(Section 1.2)

The Routine Calibration procedures are sufficient for all normal recalibration purposes, except when Pre-cal is called for (Refer to Table 1.1).

## Remote Calibration over the IEEE 488 Bus (Section 1.3)

Section 1.3 describes the device-dependent commands necessary for routine calibration of the 4200 over the IEEE 488 bus, as a supplement to Section 5 of the User's Handbook. A guideline example is given, but this needs to be adapted for the bus controller in use.

#### **Pre-calibration Procedures**

(Section 1.4)

In an initial internal calibration process at manufacture, certain "Pre-cal" parameters are established in a special calibration memory.

Under certain conditions (detailed in Table 1.1) these parameters need to be re-established by the 'Pre-Cal' procedure in Section 1.4, before the Routine Autocalibration of Section 1.2.

#### Current Option Internal Adjustment

(Section 1.5)

If the Power Supply/Current Heatsink has been changed it may be necessary to adjust the quiescent bias current ( $I_{\Omega}$ ) by internal adjustment. Refer to Section 5.4 for further information.

| Assembly                                          | Components Replaced                                                                                                                                                   | Precal<br>required                                | Routine<br>recal                     |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------|

| Digital<br>(7.2)                                  | Complete Assembly  Lithium Battery (Sect. 5.3)  Non-volatile RAM (M10/M23)  Non-volatile RAM Supply-  Commutator components                                           | Full<br>Full<br>Full                              | Full<br>Full<br>Full                 |

| Reference<br>Divider<br>(7.4)                     | Complete Assembly Reference Assembly (7.4-7)  Any set of main, guard or LSD switch FET's Reference Buffer Switch Driver Flip Flops or their preselected resistors R79 | Full<br>Full<br>Full<br>Full<br>Full              | Full<br>Full<br>Full<br>Full<br>Full |

| Output<br>Control<br>(7.5)                        | Complete Assembly                                                                                                                                                     | ·<br>-                                            | Full                                 |

| Sine<br>Source<br>(7.6)                           | Complete Assembly                                                                                                                                                     | Specification<br>Verification a<br>user's discret | t                                    |

| AC<br>(7.7)                                       | Complete Assembly  Sense Amplifier Reference Inverter AC/DC Transfer & Integrators                                                                                    | -<br>-<br>-                                       | Full<br>Full<br>Full<br>Full         |

| Current<br>(7.8)                                  | Complete Assembly  M8 and associated components Current Shunts Feedback resistor R45                                                                                  | -                                                 | All<br>I Ranges                      |

| All Other<br>Assemblies<br>Not Specified<br>Above |                                                                                                                                                                       | Specification<br>Verification a<br>user's discret |                                      |

TABLE 1.1 LIST OF CRITICAL PCBS AND COMPONENTS

#### 1.2.1 Introduction

The 4200 possesses excellent short and long term stability. Some users will wish to maintain the highest accuracy by recalibrating at short intervals (e.g. every 24 hours). In these cases, recalibration of the 4200 becomes a routine task. For this reason, Routine Autocalibration procedures are repeated in Section 8 of the User's Handbook. It is emphasized that the 4200 can be used immediately after recalibration.

#### 1.2.2 The 4200 Autocal Feature

Full or part calibration may be carried out for all routine purposes from the front panel. Removal of covers is unnecessary, therefore avoiding thermal disturbance. Calibration corrections are stored in an internal memory which remains energized by a battery even when the instrument power supply is switched off. The life of the battery is estimated at 10 years, and it is normally changed at 5 year intervals. On power-up, the 4200 performs a self-test which includes a check of the contents of the calibration memory.

#### 1.2.3 Equipment Requirements

This summary relates to the recommended method of calibrating the 4200:

#### **AC VOLTAGE**

(IV - 1000V Full Range Values and 10V Range Linearity)

An Adjustable DC Voltage Source of suitable accuracy.

Example:

Datron 4000 or 4000A Autocal Standard.

An AC/DC Thermal Transfer Standard capable of operating over the range 1V to 1100V RMS.

#### **AC VOLTAGE**

#### 2-WIRE COMPENSATION AT HIGH FREQUENCY

(1V and 10V Full Range values)

An AC voltmeter of suitable accuracy. Example: Datron 1081

#### AC MILLIVOLTS

(1mV - 100mV Full Range Values)

#### At LF and HF;

An AC DVM of suitable accuracy and frequency response.

Example:

Datron 1081 or similar.

#### at LF;

A commercially-available Inductive Voltage Divider of suitable accuracy and frequency response; with ratios of 10:1, 100:1 and 1000:1.

#### at HF:

The 4200 under test with the correction figure for 10% of its 10V Range at HF.

#### AC CURRENT

(1mA - 1A Full Range Values)

A DC Current Source of suitable accuracy, and an AC/DC Thermal Transfer complete with a set of Calibrated Thermal-Transfer Current Shunts of suitable accuracy.

#### AC CURRENT (Alternative Method)

(1uA - 1A Full Range Values)

A set of calibrated AC Shunts of suitable value and accuracy, and

An AC DVM of suitable accuracy and frequency response.

the full range voltage is present at the Thermal

Transfer Standard input terminals. On 1000V checks

this voltage is potentially lethal, so EXTREME

CAUTION must be observed when making adjustments to the Thermal Transfer Standard

During Performance checks and calibration

Example: Da

WARNING

sensitivity.

Datron 1081 or similar.

#### 1.2.3.1 Notes on the Use of the Thermal Transfer

Four points are important:

#### 1. Start with OUTPUT OFF.

The 4200 should be connected to the Thermal Transfer Standard only when the 4200 OUTPUT OFF LED is lit. (With Output OFF, the I+, I-, Hi and Lo terminals are at high impedance).

#### CAUTION

3.

The Thermal Transfer Standard used must be able to withstand peak voltages up to 1600V between its input terminals. Such voltages may be present during the time that the 4200 is ramping from zero to 1100V Full Scale after setting OUTPUT ON.

#### 2. Sensitivity.

Always set the Thermal Transfer Standard to its lowest sensitivity before connecting up. Increase sensitivity when necessary to obtain the required input level.

#### 1.2.4 Interconnections

Interconnection instructions in this section are necessarily simple and basic. It is recognised that they may need to be adapted to meet an individual user's requirements.

It is assumed that users will possess knowledge of the operation and use of standards equipment.

#### 1.2.5 Calibration Modes

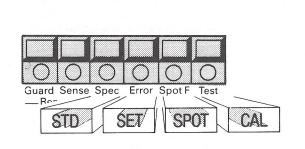

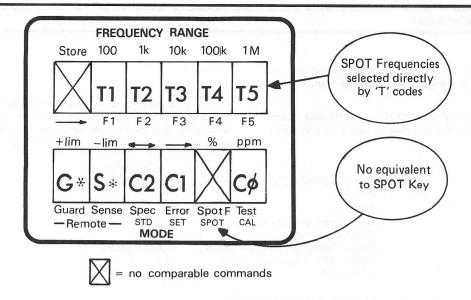

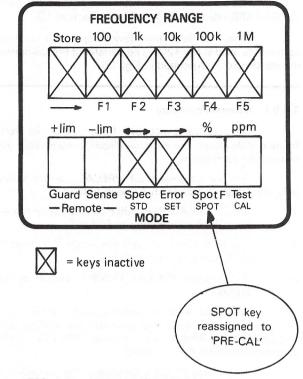

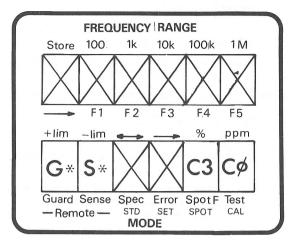

Special keys are used in the Autocal mode. They are illustrated below:

The three keys labelled **STD**, **SET** and **SPOT** preselect alternative calibration modes. To finally implement any calibration, the **CAL** key must be pressed.

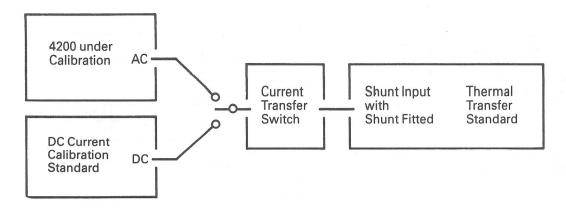

Fig. 1.1 CALIBRATION MODES

These keys are activated by a simple procedure:

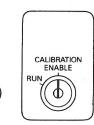

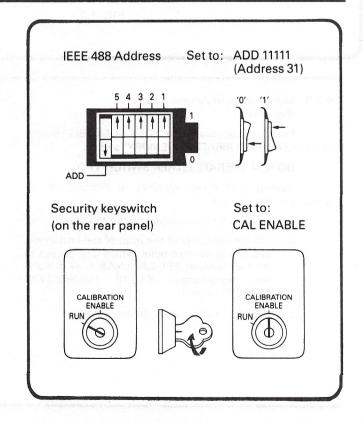

On the rear panel there are two switches: the IEEE 488 address switch, and a security keyswitch labelled 'RUN/CAL ENABLE'.

By setting the address switch to 31 (ADD 11111) for Front Panel calibration, and the keyswitch to CAL ENABLE; four of the front panel 'MODE' keys are reassigned to calibration functions, permitting access to the correction memories.

When these modes are active, the legend 'cal' is presented on the MODE display.

#### 1.2.5.1 General Procedure

The OUTPUT display is set to the Calibration Standard value, the 4200 output is switched ON, and one of the calibration mode preselector keys (STD, SET or SPOT) is

pressed. The 4200 output is adjusted to equal the Calibration Standard value, and the CAL key is pressed to execute the calibration.

#### 1.2.5.2 Autocal Facilities

SET The SET key allows calibration to any value between 20% and 200% of nominal Full Range value (20% to 110% on 1000V range). If, for instance, an adjustable DC voltage standard is not available, the SET key permits the 4200 to be calibrated against a Thermal Transfer standard whose reference is a buffered bank of Standard Cells.

SPOT When SPOT is pressed, the 4200 assumes that the spot frequency is to be changed, and so defaults frequency to 1kHz. When used with SET, SPOT calibration can be carried out within 10% of full range value, but when SPOT is used without SET, the 4200 assumes that the calibration is to be at Full Range. After SPOT calibration, selecting Spot F at the calibrated value achieves the highest possible specification. For Recall procedures see the User's Handbook Section 4, page 4-11.

STD The STD key allows a user to trim the value of the internal Master Reference voltage. The facility can be used to correct for any long term drift, or to avoid a full recalibration of the 4200 when Laboratory References have been re-standardized. STD calibration effectively changes the gain of all voltage and current ranges in the same ratio, by a simple procedure available on either the 1V or 10V range.

CAL The CAL key executes, then cancels, the preselected AUTOCAL mode.

CAL If the CAL key is pressed without first pressing SET, only SPOT or STD, the 4200 assumes that the selected range is to be calibrated at the exact Full Range, at either LF or HF or both.

#### 1.2.6 General Notes

Remote Sense is available as follows:

1V 10V 100V 1000V - Local/Remote Sense

1mV 10mV 100mV - Local Sense only

All current ranges - not applicable

(Local = 2-wire sense: Remote = 4-wire sense)

Output must be OFF to change sense connection (except that Remote changes automatically to Local when switching to Millivolt Ranges).

On 1V and 10V ranges a Local/Remote difference correction can be stored; for the calibration procedure refer to Section 1.2.9.

#### Upranging — OUTPUT OFF Default.

The 4200 cannot enter High-Voltage State (>75V) with OUTPUT ON. Consequently, when ranging-up, the operating system allows the upranging to occur, but defaults to OUTPUT OFF for two specific cases:

- a. When upranging to the 1000V Range,

- b. When upranging to the 100V Range; to a voltage of 75V or more.

Otherwise, OUTPUT remains ON when changing OUTPUT RANGE (refer to User's Handbook Section 4, pages 4-7 and 4-8).

**High Frequency Calibrations.** Several iterations may be required to achieve satisfactory calibration; particularly if the initial errors are large, or if the Transfer System being used imposes a long calibration time.

Repeat the procedure as necessary.

**1000V Range Calibration Sequence:** LF calibration must be completed first. However HF1/HF2 bands may, if the user requires, be calibrated in reverse order.SET mode must be used for 700V/HF2.

**SPOT Memory Erasure.** To prevent unwanted calibrations at unused spot frequencies, it is possible to 'Uncalibrate' any spot frequency on any range. The procedure is:

Select **Zero** Output, set **OUTPUT ON** and Press **CAL**. When the CAL-ENABLE/RUN Switch is set to RUN, any subsequent selection of that particular Spot F will cause the message 'SFX----' to appear on the MODE/FREQUENCY display (X is the store number). This indicates that the spot is uncalibrated.

#### 1.2.7 Calibration Sequence

The sequence of operations for full calibration of the 4200 Autocal Standard is given below:

| Preparation            | Section 1.2.7.1 |

|------------------------|-----------------|

| AC Voltage             | 1.2.8           |

| 2-wire HF compensation | 1.2.9           |

| AC Current             | 1.2.10          |

| Return to use          | 1.2.7.2         |

|                        |                 |

WARNING: During performance checks and calibration a common mode voltage equal to the full range voltage may be present at the Thermal Transfer input terminals. On 1000V checks this voltage is potentially lethal, so EXTREME CAUTION must be observed when making adjustments to the Thermal Transfer sensitivity.

CAUTION: The Thermal Transfer Standard used must be able to withstand peak voltages up to 1600V between its input terminals. Such voltages may be present during the time that the 4200 is ramping from zero to 1100V Full Scale after setting OUTPUT ON.

#### 1.2.7.1 Preparation

Before any calibration from the front panel is carried out, prepare the 4200 as follows:

- Turn on the instrument to be checked and allow minimum of 4 hours to warm-up in the specified environment.

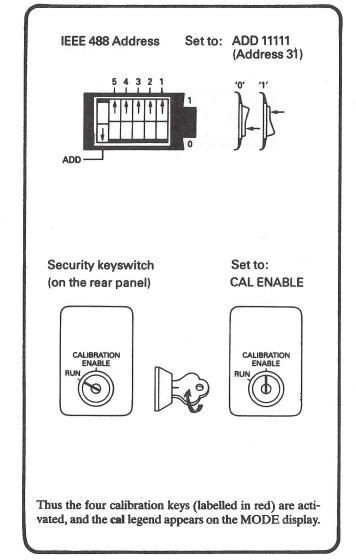

- 2. IEEE 488 Address switch: Set to ADD 11111 as shown (Address 31).

- 3. CALIBRATION ENABLE Key switch (Rear Panel). Insert Calibration Key and turn to ENABLE.

These actions activate the four calibration modes (labelled in red), and present the 'cal' legend on the MODE display.

4. Ensure that the OUTPUT OFF LED is lit.

#### 1.2.7.2 Return to Use

When any calibration is completed, return the 4200 to use as follows:

- 1. Ensure that the OUTPUT OFF LED is lit.

- 2. CALIBRATION ENABLE key switch (Rear Panel): Turn to RUN and remove the calibration key.

- IEEE 488 Address switch:

Restore to the correct address if the 4200 is to be used in an IEEE 488 system.

The activation procedure is illustrated below:

IEEE 488 Address Set to: ADD 11111 (Address 31)

Security keyswitch (on the rear panel)

Set to: CAL ENABLE

Thus the four calibration keys (labelled in red) are activated, and the cal legend appears on the MODE display.

#### The activation procedure is illustrated below:

1.2.8 AC Voltage Full Range Calibration (1V-1000V)

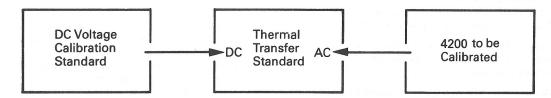

(Using Thermal Transfer Standard and DC Calibration Standard)

Calibrate the 4200 at or close to the calibration points in the table, selecting SET and/or SPOT as required as part of the following procedure:  $\frac{1}{2} \frac{1}{2} \frac{1$

#### **WARNING:**

THE TERMINALS MARKED WITH THE SYMBOL CARRY THE OUTPUT OF THE 4200. THESE TERMINALS AND ANY OTHER CONNECTIONS TO THE LOAD UNDER TEST COULD CARRY LETHAL VOLTAGES. UNDER NO CIRCUMSTANCES SHOULD USERS TOUCH ANY OF THE FRONT (OR REAR) PANEL TERMINALS UNLESS THEY ARE FIRST SATISFIED THAT NO DANGEROUS VOLTAGE IS PRESENT.

#### Note

Any existing stored HF 2-wire compensation is cleared during normal 4-wire HF calibration. The procedure in Section 1.2.9 allows a user to re-establish HF compensation for 2-wire measurement.

Nominal Cal. Points for 1V to 1000V Ranges.

|             | P. C. |                                       |                                      |                                 |

|-------------|-------------------------------------------|---------------------------------------|--------------------------------------|---------------------------------|

|             | DC<br>Standard<br>OUTPUT<br>Voltage       | 4200<br>OUTPUT<br>RANGE/<br>FREQUENCY | 4200<br>Nominal<br>OUTPUT<br>Voltage | Freq.<br>Band<br>set by<br>4200 |

|             | 1.000000V                                 | 1V 1kHz                               | 1.000000V                            | LF                              |

|             | 1.000000V                                 | 1V 1MHz                               | 1.000000V                            | HF                              |

|             | 10.00000V                                 | 10V 1kHz                              | 10.00000V                            | LF                              |

|             | 10.00000V                                 | 10V 1MHz                              | -10.00000V                           | HF                              |

| designation | 100.0000V                                 | 100V 1kHz                             | 100.0000V                            | LF                              |

|             | 100.0000V                                 | 100V 100kHz                           | 100.0000V                            | HF                              |

|             | 1000.000V                                 | 1000V 1kHz                            | 1000.000V                            | LF                              |

|             | 1000.000V                                 | 1000V 30kHz                           | 1000.000V                            | HF1                             |

#### 700V at 100kHz:

'SET' Calibration must be employed.

| District State of the last of |         |         |         |       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|-----|

| 700.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000V 10 | 00V 100 | kHz 700 | .000V | HF2 |

4200 & DC Voltage Standard

With OUTPUT OFF, connect to the Thermal Transfer

AC and DC inputs, respectively.

Thermal Transfer Standard

Configure for DC measurement at the required Calibration Voltage.

DC Voltage Calibration Standard Set to the Cal. voltage, OUTPUT ON.

#### 4. Thermal Transfer Standard

- a. Adjust for Null at the Cal. Voltage.

- b. Configure for AC measurement at the Cal. Voltage.

#### 5. 4200

- a. On AC FUNCTION, select the required OUTPUT

- Select the required FREQUENCY RANGE (or if a Spot Frequency is to be calibrated: Press SPOT and select F1 - F5).

- c. Use FREQUENCY | keys to display the required Cal. Frequency.

- d. Use OUTPUT | | keys to display the required Cal. Voltage (if at Nominal Full Range, merely press the Full Range key).

- e. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- f. Use the OUTPUT †|| keys to adjust the OUTPUT Display reading to obtain a null on the Thermal Transfer.

- Execute the calibration by pressing the CAL key (and if calibrating a Spot Frequency, repress the SPOT key to deselect).

Calibration of HF 2-wire Compensation

On the 1V and 10V ranges there are two HF calibration memories. One holds the correction value obtained during Remote Sense (4-wire) 'wideband' calibration; the other contains a 2-wire HF compensation value which is added to the wideband correction, when Remote Sense is not selected (local sense).

During a 4-wire HF calibration on the 1V or 10V range, the stored HF 2-wire compensation value is cleared to zero. Any 4-wire HF calibration to be performed must therefore be completed before the 2-wire compensation is executed.

Calibrate the 4200 at or close to the calibration points in the table, selecting SET as required.

#### Nominal Cal. Points for 2-wire HF Compensation.

| DC<br>Standard<br>OUTPUT<br>Voltage | 4200<br>OUTPUT<br>RANGE/<br>FREQUENCY | 4200<br>Nominal<br>OUTPUT<br>Voltage | Freq.<br>Band<br>set by<br>4200 |

|-------------------------------------|---------------------------------------|--------------------------------------|---------------------------------|

| 1.000000V                           | 1V 1MHz                               | 1.000000V                            | HF                              |

| 10.00000V                           | 10V 1MHz                              | 10.00000V                            | HF                              |

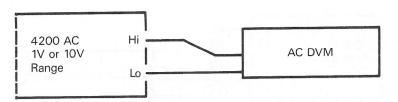

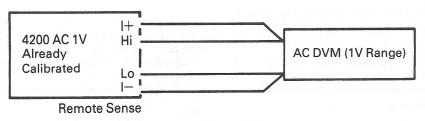

# 4200 & AC Voltmeter With 4200 OUTPUT OFF, make 4-wire connections between the 4200 and the AC DVM.

# 2. AC Voltmeter Configure for AC measurement at the required Calibration Voltage.

# 4200 a. On AC FUNCTION, select the rec

- a. On AC FUNCTION, select the required OUTPUT RANGE.

- b. Select the required FREQUENCY RANGE.

- c. Use the FREQUENCY †|| keys to display the required Calibration Frequency.

- d. Use the OUTPUT † keys to display the required Calibration Voltage.

(If at Nominal Full Range, merely press the Full Range key.)

#### 4. HF 2-wire Calibration Sequence

- a. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- b. Record the DVM reading.

- c. Set 4200 OUTPUT OFF.

- d. On the 4200 deselect Remote Sense.

- e. Connect the DVM to the 4200 Hi and Lo terminals for 4-wire measurement of the 4200 2-wire output.

- f. Set 4200 OUTPUT ON.

- g. Use the 4200 OUTPUT † keys to display the DVM reading recorded at (b).

- h. Press 'CAL'

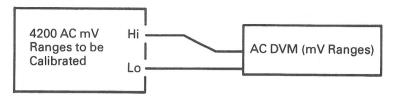

#### Standardization of DVM Millivolt Ranges

#### Calibration of 4200 LF Millivolt Ranges

Calibrate the 4200 at or close to the calibration points in the table, selecting SET and/or SPOT as required, as part of the following procedure:

#### Note:

It is assumed that for a SPOT calibration, the 1V Range has already been Spot calibrated at the required calibration point.

#### 1. 4200, IVD and AC DVM

With OUTPUT OFF, connect the circuit for Standardization.

#### 2. IVD

Set the ratio as required for the Millivolt Range to be calibrated.

#### AC DVM

Configure for measurement at the required Calibration Point.

#### 4. 4200

- a. On AC FUNCTION, select 1V RANGE.

- Select the required FREQUENCY RANGE (or if a Spot Frequency is to be calibrated: Press SPOT and select F1 - F5).

- c. Use FREQUENCY †| keys to display the required Calibration Frequency.

- d. Use OUTPUT 1 keys to display the required IVD input voltage.

(If at Nominal Full Range, merely press the Full Range key.)

- e. Set OUTPUT ON; note DVM reading as 'V1'.

- Set OUTPUT OFF, and reconnect the circuit for Calibration.

- Select the required Millivolt OUTPUT RANGE.

- h. Use OUTPUT †|| keys to set the Calibration Voltage on the OUTPUT Display.

(If at Nominal Full Range, merely press the Full Range key.)

- j. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- k. Use the 111 keys to adjust the OUPUT Display reading to obtain 'V1' on the DVM.

- Execute the calibration by pressing the CAL key (and if calibrating a Spot Frequency, repress the SPOT key to deselect). Set OUTPUT OFF.

#### Nominal Cal. Points for Millivolt Ranges.

| IVD Ratio<br>(1V Range<br>to<br>mV Range) | 420<br>OUTP<br>RANG<br>FREQUE | PUT<br>GE/ | 4200<br>Nominal<br>OUTPUT<br>Voltage | Freq.<br>Band<br>set by<br>4200 |

|-------------------------------------------|-------------------------------|------------|--------------------------------------|---------------------------------|

| 10 : 1                                    | 100mV                         | 1kHz       | 100.0000mV                           | LF                              |

| 100 : 1                                   | 10mV                          | 1kHz       | 10.0000mV                            | LF                              |

| 1000 : 1                                  | 1mV                           | 1kHz       | 1.0000mV                             | LF                              |

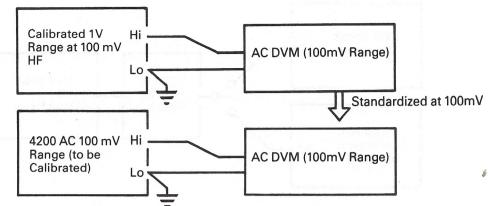

Standardization of DVM 100mV Range (on 1V Range only, use 4-wire connection in Remote Sense)

4200 HF 100mV Range

Calibration of

N.B.

These Calibrations are not fully traceable. Calibrate the 4200 at or close to the calibration points in the table, selecting SET and/or SPOT as required, as part of the following procedure:

#### Note:

It is assumed that the 1V and 10V Ranges have been Wideband-calibrated (and for SPOT calibration, the 1V Range has already been Spot calibrated) at the required HF calibration points.

#### Nominal Cal. Points for HF Millivolt Ranges.

| 4200<br>OUTPUT<br>RANGE/<br>FREQUENCY |      | 4200<br>Nominal<br>OUTPUT<br>Voltage | Freq.<br>Band<br>set by<br>4200 |

|---------------------------------------|------|--------------------------------------|---------------------------------|

| 100mV                                 | 1MHz | 100.0000mV                           | HF                              |

| 10mV                                  | 1MHz | 10.0000mV                            | HF                              |

| 1mV                                   | 1MHz | 1.0000mV                             | HF                              |

#### 1. 4200 and AC DVM

Measure 10.00000V output on the 10V Range at the HF Calibration Frequency using the Thermal Transfer.

Note the reading: call it 'V1'.

Measure 1.00000V output on the 10V Range at the HF Calibration Frequency using the Thermal Transfer.

Note the reading: call it 'V2'.

c. Divide V1 by V2; divide the result by 10. This gives the 10% Range Correction Factor, 'C'.

$$C = \frac{V1}{10 \times V2}$$

This factor subsequently corrects a DVM measurement at 10% of one range, to standardize the DVM for calibration of the next millivolt range down.

d. With OUTPUT OFF, connect the circuit for Standardization.

#### 2. 4200

- a. On AC FUNCTION, select 1V OUTPUT RANGE.

- Select the required FREQUENCY RANGE (or if a Spot Frequency is to be calibrated: Press SPOT and select F1 - F5).

- Use FREQUENCY || keys to display the required Calibration Frequency.

- d. Using the OUTPUT 11 keys, adjust the OUTPUT Display to the 100mV Calibration Voltage on the 1V Range.

- Set the 4200 OUTPUT ON and note the DVM reading. Multiply the reading by 'C', and note the results as 'Vc'.

(If the DVM being used is a Datron Autocal instrument, the Maths function can do this automatically.)

- f. With OUTPUT OFF, connect the circuit for Calibration.

- g. Set 4200 OUTPUT OFF, select 100mV Range, and again use the OUTPUT | keys to set the OUTPUT Display to the Calibration Voltage. (If at Nominal Full Range, merely press the Full Range key).

- h. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- j. Adjust the OUTPUT || keys for a reading of 'Vc' on the DVM.

- Execute the calibration by pressing the CAL key (and if calibrating a Spot Frequency, re-press the SPOT key to deselect). Set OUTPUT OFF.

- Repeat operations 2 (a) to (k), selecting 10mV on the 100mV Range to standardize the DVM, and calibrating the 10mV Range, using the same correction factor 'C'.

- m. Repeat operations 2 (a) to (k), selecting 1mV on the 10mV Range to standardize the DVM, and calibrating the 1mV Range, using the same correction factor 'C'.

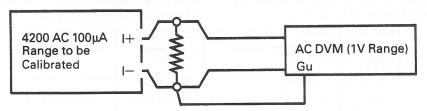

Calibrate the 4200 at or close to the calibration points in the table, selecting SET and/or SPOT as required, as part of the following procedure:

Calibrate 1mA Range only if the Thermal Transfer is adequately calibrated at these levels.

#### 1. Thermal Transfer Standard

Configure for DC measurement at the required Calibration Current and connect the appropriate shunt.

#### 2. DC Current Standard

- a. With OUTPUT OFF, connect across the Thermal Transfer shunt, and set to the required Calibration Current.

- b. Set OUTPUT ON.

#### 3. Thermal Transfer Standard

Adjust for null at the Calibration Current.

#### 4. DC Current Standard

- a. Set OUTPUT OFF.

- b. Disconnect from the shunt.

#### 5. 4200

- With OUTPUT OFF, connect the I+ and Iterminals across the Shunt.

- On I FUNCTION, select the required OUTPUT RANGE.

- Select the required FREQUENCY RANGE (or if a Spot Frequency is to be calibrated: Press SPOT and select F1 — F5).

- d. Use FREQUENCY † keys to display the required Calibration Frequency.

- e. Use OUTPUT † keys to display the required Calibration Current.

(If at Nominal Full Range, press the Full Range key.)

- f. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- g. Use the OUTPUT 111 keys to adjust the OUTPUT Display reading to obtain a null on the Thermal Transfer.

- Execute the calibration by pressing the CAL key (and if calibrating a Spot Frequency, repress the SPOT key to deselect). Set OUTPUT OFF.

#### Nominal Cal. Points for 1mA to 1A Ranges.

| DC<br>Standard<br>OUTPUT<br>Current | 420<br>OUTI<br>RAN<br>FREQU | PUT<br>GE/ | 4200<br>Nominal<br>OUTPUT<br>Current | Freq.<br>Band<br>set by<br>4200 |

|-------------------------------------|-----------------------------|------------|--------------------------------------|---------------------------------|

| 1.000000mA                          | 1mA                         | 300Hz      | 1.000000mA                           | LF                              |

| 1.000000mA                          | 1mA                         | 5kHz       | 1.000000mA                           | HF                              |

| 10.00000mA                          | 10mA                        | 300Hz      | 10.00000mA                           | LF                              |

| 10.00000mA                          | 10mA                        | 5kHz       | 10.00000mA                           | HF                              |

| 100.0000mA                          | 100mA                       | 300Hz      | 100.0000mA                           | LF                              |

| 100.000mA                           | 100mA                       | 5kHz       | 100.0000mA                           | HF                              |

| 1.000000A                           | 1A                          | 300Hz      | 1.000000A                            | LF                              |

| 1.000000A                           | 1A                          | 5kHz       | 1.000000A                            | HF                              |

#### Standardization of DVM 1V Range

**Calibration of 4200 Current Ranges**

Calibrate the 4200 at or close to the calibration points in the table, selecting SET and/or SPOT as required, as part of the following procedure:

#### Note

It is assumed that for a SPOT calibration, the 1V Range has already been Spot calibrated at the required calibration point.

#### Nominal Cal. Points for $100\mu A$ to 1A Ranges.

| 4200<br>OUTPUT<br>RANGE/<br>FREQUENCY | 4200<br>Nominal<br>OUTPUT<br>Current | Freq.<br>Band<br>set by<br>4200 |

|---------------------------------------|--------------------------------------|---------------------------------|

| 100μA 300Hz                           | 100.0000μΑ                           | LF                              |

| 100μA 5kHz                            | 100.0000μΑ                           | HF                              |

| 1mA 300Hz                             | 1.00000mA                            | LF                              |

| 1mA 5kHz                              | 1.00000mA                            | HF                              |

| 10mA 300Hz                            | 10.0000mA                            | LF                              |

| 10mA 5kHz                             | 10.00000mA                           | HF                              |

| 100mA 300Hz                           | 100.000mA                            | LF                              |

| 100mA 5kHz                            | 100.0000mA                           | HF                              |

| 1A 300Hz                              | 1.00000A                             | LF                              |

| 1A 5kHz                               | 1.00000A                             | HF                              |

#### 1. 4200 and AC DVM

With OUTPUT OFF, connect the 4200 and DVM for Standardization.

Select the 1V Range on the AC DVM.

#### 2. 4200

- Set to the 1V Range at the Calibration Frequency and adjust for calibrated 1.000000V output.

- Set OUTPUT ON and note the DVM reading as 'V1'.

- Set OUTPUT OFF, and reconnect the test circuit for Calibration, using the correct shunt for the range to be calibrated.

- d. On I FUNCTION, select the required OUTPUT RANGE.

- Select the required FREQUENCY RANGE (or if a Spot Frequency is to be calibrated: Press SPOT and select F1 - F5).

- f. Use FREQUENCY † keys to display the required Calibration Frequency.

- g. Use OUTPUT † keys to display the required Calibration Current.

(If at Nominal Full Range, press the Full Range key).

- h. Set 4200 OUTPUT ON (and if NOT at Nominal Full Range, Select SET).

- Use the OUTPUT H keys to adjust the OUTPUT Display reading to obtain a DVM reading of 'V1'.

- Execute the calibration by pressing the CAL key (and if calibrating a Spot Frequency, repress the SPOT key to deselect). Set OUTPUT OFF.

#### 1.3.1 Introduction

The operation of the 4200 in systems applications, via the IEEE 488 interface, is described in Section 5 of the User's Handbook.

In addition to its capability as a programming calibrator, the 4200 can itself be calibrated under remote

control. Full autocalibration of the instrument over the bus implies availability of programmable standards, a programmable thermal transfer standard and a suitably-programmed controller.

#### 1.3.2 Calibration Commands

Table 1.2 lists the device-dependent calibration commands used in the 4200. The transfer of calibration facilities to remote control is illustrated in Fig. 1.2.

#### Note

With the Calibration keyswitch set to ENABLE, the  ${\rm 'I'}$  code (User's Aide-Memoire) accesses an alpha-numeric store for up to 16 ASCII characters.

| Command<br>Codes                         |                                                                                                                         | AUTOCAL Mode                                                  | AC Voltage<br>(AC)        | AC Current |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|------------|

| СФ                                       | only (at nominal FR)  SET Gain for range at user's selected                                                             |                                                               | ALL RANGES                | ALL RANGES |

| C1<br>and<br>CØ                          |                                                                                                                         |                                                               | ALL RANGES                | ALL RANGES |

| C2<br>and<br>CØ                          | į į                                                                                                                     | STD<br>and<br>GAIN CAL                                        | 1V and 10V<br>Ranges only | · –        |

| C3<br>and<br>CØ                          |                                                                                                                         | PRECAL<br>and<br>GAIN CAL                                     | 10V Range                 | -          |

| T1<br>to<br>T5<br>and<br>CØ              |                                                                                                                         | Spot Frequency 1<br>to<br>Spot Frequency 5<br>and<br>GAIN CAL | ALL RANGES                | ALL RANGES |

| T1<br>to<br>T5<br>and<br>C1<br>and<br>CØ | Spot Frequency 1 to Spot Frequency 5 and Gain for range at User's selected value  Cancel Spot Frequency  User's Message |                                                               | ALL RANGES                | ALL RANGES |

| тø                                       |                                                                                                                         |                                                               | ALL RANGES                | ALL RANGES |

| I                                        |                                                                                                                         |                                                               | See para                  | а. 1.3.2   |

TABLE 1.2 AVAILABILITY OF COMMAND CODES

These commands can only be activated when two conditions have been fulfilled:

- The CALIBRATION ENABLE keyswitch on the 4200 Rear Panel must be set to ENABLE.

- The IEEE Interface command-code W1 must have been received and activated.

In addition the bus command C3 (PRECAL) can only be activated when the internal 'PRE-CAL ENABLE' switch is enabled.

When the 4200 is under remote control over the bus, the command code  $W\emptyset$  overrides the settings of the CALIBRATION ENABLE and internal PRE-CAL ENABLE switches, disabling the 'C' codes.

FIG. 1.2 TRANSFER OF CALIBRATION FACILITIES TO REMOTE CONTROL

#### 1.3.2.1 General Procedure

The Main Register is set to the Calibration Standard value (M\*\*\*...), the 4200 Output is switched ON (O1), and one or a specified sequence of the calibration mode command codes (C1, C2, C3, I, T1-T5) may be transmitted.

The 'M' Code is adjusted to obtain a null at the Calibration Standard value, and CØ is transmitted to execute the calibration.

#### 1.3.2.2 Command Code Facilities

C1 (SET)

C1 allows calibration to any value between 20% and 200% of nominal Full Range value (20% to 110% on 1000V range). If, for instance, an adjustable DC voltage standard is not available, C1 permits the 4200 to be calibrated against a Thermal Transfer standard whose reference is a buffered bank of Standard Cells.

C2 (STD) C2 allows a user to trim the value of the internal Master Reference voltage. The facility can be used to correct for any long-term drift, or to avoid a full recalibration of the 4200 when Laboratory References have been re-standardized.